4-Gbit光纖通道數字時鐘晶振設計的挑戰

來源:http://m.robbia.com.cn 作者:泰河電子 2019年01月17

4-Gbit光纖通道數字時鐘晶振設計的挑戰

低抖動晶振傳輸信號考慮因素適用于任何高速和高頻時鐘分配系統,高頻晶振電子產品要低定時抖動,不僅抖動特性差影響數據錯誤,但也可能導致失敗使用信號源作為參考的鎖相環,因此,當設計師接近項目時將一個高速數字應用于程序,他們需要考慮各種信號完整性低速時不需要的規定應用程序,規劃高速數字化的關鍵挑戰項目包括大限度地減少定時抖動,本文要提到的是高速數字時鐘設計的挑戰生成和分配工作.

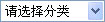

在更高的速度,傳輸線和他們的組件表現不同他們以較低的速度做,產生這樣的信號完整性問題,如抖動,噪聲,反射和如果沒有正確指定和配置串擾,如果源要用作顯示時鐘參考,結果將是模糊的顯示,通常,時鐘晶振信號通過的速度越快過渡區域,系統抖動越小生產(見圖1),減少排放,在高速應用中,產生電磁干擾的可能性(EMI)急劇增加,FCC規定關于EMI降噪正在變得越來越多更快的數字速度更嚴格. 設計師需要解決傳輸等特性線,差分信號,信號幅度和諧波含量以最大化能量將被送到負載,從而減少能量排放量,確保穩定,一般來說,越高規定的電子工作頻率你正在設計的系統,越關鍵時鐘穩定性是,時鐘性能不穩定會導致誤碼率增加,錯誤無論是數據系統中的數據還是錯過的數據它們是本地或廣域系統,傳輸線阻抗匹配,該整個傳輸的阻抗和長度必須測量線并與每個線匹配終止,如果忽略阻抗匹配,可能發生發射,串擾和反射.

實現最佳系統性能的關鍵在高速應用程序開始有效時鐘生成和分配的設計方法,簡而言之,設計師應該采用一個解決各種時鐘生成的方法和分配組件一樣完整解決方案,而不是單個部分,小心關注選擇適當的組件和電路分配方法應在項目的開始,牢記相互關系組件彼此之間,進一步,考慮特征阻抗很重要的所有有源晶振和無源晶振元件隨著設計的進展,操作頻率.

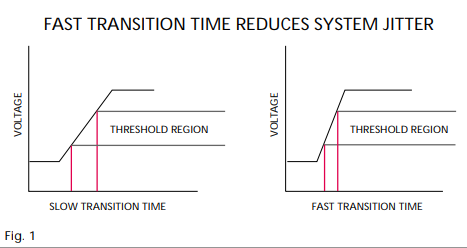

電源考慮因素,首要考慮因素這是為了確保時鐘無噪音,低電源消耗今天的要求也在增加更高速的系統,正確選擇以下時鐘生成和分配組件是必不可少的(見圖2):1.石英晶體振蕩器及其輸出邏輯2.時鐘驅動程序,在某些情況下會包含啟用功能3.5V或3V電源的CMOS轉換器傳輸線(雙絞線,同軸電纜,PCB走線)本白皮書旨在幫助您制作有關這些時鐘生成的明智決定接近你的時候和分配組件下一個高速數字系統設計.

石英晶體振蕩器和邏輯選擇選擇合適的晶體振蕩器是在高速應用中至關重要,因為它將提供時鐘參考全時鐘分配系統,通常是嚴格的晶體振蕩器應用要求頻率穩定性為±20ppm,快速上升并且下降時間小于600皮秒,低特征抖動和正耦合發射極邏輯PECL差分輸出,頻率穩定性將提供可靠的系統參考,而波形的快速上升和下降時間將會導致系統抖動低,(雖然飽和了可以引入快速上升和下降時間的過渡不需要的噪音,這種噪音將被取消使用差分信號.)

石英晶體振蕩器和邏輯選擇選擇合適的晶體振蕩器是在高速應用中至關重要,因為它將提供時鐘參考全時鐘分配系統,通常是嚴格的晶體振蕩器應用要求頻率穩定性為±20ppm,快速上升并且下降時間小于600皮秒,低特征抖動和正耦合發射極邏輯PECL差分輸出,頻率穩定性將提供可靠的系統參考,而波形的快速上升和下降時間將會導致系統抖動低,(雖然飽和了可以引入快速上升和下降時間的過渡不需要的噪音,這種噪音將被取消使用差分信號.)

晶體振蕩器質量除了確保波形中的低抖動外,設計人員應確保抖動最小化在振蕩器本身,這是通過選擇來實現的包含非常高Q值振蕩器,此外,晶體應調整到振蕩器電路由振蕩器優化制造商,因為振蕩器特性隨負載阻抗而變化和負載偏置電壓,重要的是指定正在使用的實際負載和通信設備,這對晶振供應商來說時鐘驅動的另一個方面應該是結構性設備的對稱性,這反映在整體信號穩定性更好.

低抖動晶振傳輸信號考慮因素適用于任何高速和高頻時鐘分配系統,高頻晶振電子產品要低定時抖動,不僅抖動特性差影響數據錯誤,但也可能導致失敗使用信號源作為參考的鎖相環,因此,當設計師接近項目時將一個高速數字應用于程序,他們需要考慮各種信號完整性低速時不需要的規定應用程序,規劃高速數字化的關鍵挑戰項目包括大限度地減少定時抖動,本文要提到的是高速數字時鐘設計的挑戰生成和分配工作.

在更高的速度,傳輸線和他們的組件表現不同他們以較低的速度做,產生這樣的信號完整性問題,如抖動,噪聲,反射和如果沒有正確指定和配置串擾,如果源要用作顯示時鐘參考,結果將是模糊的顯示,通常,時鐘晶振信號通過的速度越快過渡區域,系統抖動越小生產(見圖1),減少排放,在高速應用中,產生電磁干擾的可能性(EMI)急劇增加,FCC規定關于EMI降噪正在變得越來越多更快的數字速度更嚴格. 設計師需要解決傳輸等特性線,差分信號,信號幅度和諧波含量以最大化能量將被送到負載,從而減少能量排放量,確保穩定,一般來說,越高規定的電子工作頻率你正在設計的系統,越關鍵時鐘穩定性是,時鐘性能不穩定會導致誤碼率增加,錯誤無論是數據系統中的數據還是錯過的數據它們是本地或廣域系統,傳輸線阻抗匹配,該整個傳輸的阻抗和長度必須測量線并與每個線匹配終止,如果忽略阻抗匹配,可能發生發射,串擾和反射.

實現最佳系統性能的關鍵在高速應用程序開始有效時鐘生成和分配的設計方法,簡而言之,設計師應該采用一個解決各種時鐘生成的方法和分配組件一樣完整解決方案,而不是單個部分,小心關注選擇適當的組件和電路分配方法應在項目的開始,牢記相互關系組件彼此之間,進一步,考慮特征阻抗很重要的所有有源晶振和無源晶振元件隨著設計的進展,操作頻率.

電源考慮因素,首要考慮因素這是為了確保時鐘無噪音,低電源消耗今天的要求也在增加更高速的系統,正確選擇以下時鐘生成和分配組件是必不可少的(見圖2):1.石英晶體振蕩器及其輸出邏輯2.時鐘驅動程序,在某些情況下會包含啟用功能3.5V或3V電源的CMOS轉換器傳輸線(雙絞線,同軸電纜,PCB走線)本白皮書旨在幫助您制作有關這些時鐘生成的明智決定接近你的時候和分配組件下一個高速數字系統設計.

晶體振蕩器質量除了確保波形中的低抖動外,設計人員應確保抖動最小化在振蕩器本身,這是通過選擇來實現的包含非常高Q值振蕩器,此外,晶體應調整到振蕩器電路由振蕩器優化制造商,因為振蕩器特性隨負載阻抗而變化和負載偏置電壓,重要的是指定正在使用的實際負載和通信設備,這對晶振供應商來說時鐘驅動的另一個方面應該是結構性設備的對稱性,這反映在整體信號穩定性更好.

正在載入評論數據...

相關資訊

- [2023-07-12]康納溫菲爾德推出符合Stratum3E...

- [2023-06-26]選擇石英晶體要了解的必要參數,...

- [2023-06-25]艾伯康公司發布連續電壓有源晶振...

- [2021-01-18]今日主題:什么樣性能的石英晶振...

- [2021-01-13]是什么原因造成晶振相噪惡化?都...

- [2020-12-09]干貨干貨!愛普生旗下SG-8018系列...

- [2020-09-08]石英Crystal工作原理是怎樣的,這...

- [2020-09-01]Oscillator的制造流程究竟是怎樣...